摘要:介绍了基于龙芯2号的PC104 Plus处理器模块的设计方案。该方案以龙芯2号为核心,符合PC104 Plus总线规范,并针对模块中电源设计、复住时序、时钟电路及信号完整性等关键问题给出了相应的解决方法。基于该方案的处理器模块已研制成功并应用于一航空电子视频记录仪中。

关键词:龙芯2号PC104 Plus总线嵌入式计算机信号完整性

PC104 Plus标准由IEEE标准化组织于1997年制定,对原PC104标准进行了扩展。PC104 Plus总线由两部分组成,分别与PCI总线和ISA总线完全兼容。该标准制定了一种体积小、功耗低、连接灵活的嵌入式总线规范。由于其具有超小型、高集成度、高可靠性等特点,目前已被广泛应用于工业控制、航空航天、军事等领域中。

龙芯2号是中国科学院计算技术研究所自主研发的国内首款64位高性能通用CPU,已经批量生产的龙芯2C (Godson 2C]CPU经实测性能达到了奔腾3系列500MHz水平。基于龙芯2号设计相应的PC104 Plus处理器模块,将填补我国通用处理器在PCI04 Plus产品领域的空白,为国产通用处理器的应用提供一个新的途径。对比市场上基于x86体系结构的对应产品,龙芯2号由于采用了RISC体系结构,具有高性能、低功耗等特点,因此基于龙芯2号的PC104 Plus处理器模块将有很大的优势和很高的性价比。

1 系统设计

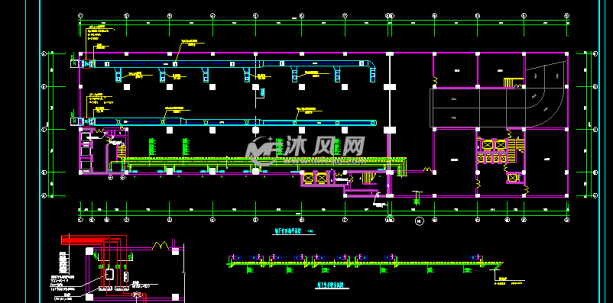

PC104 Plus处理器模块是一个小型化但功能完整的CPU主板系统,在设计时必须为龙芯2号选择相应的北桥和南桥等配套芯片。龙芯2号采用了工业标准的64位SYSAD系统总线接口,因此相应地选用了Marvell公司的GT64240A作为JPC104 Plus处理器模块中龙芯2号的配套北桥。在系统中,南桥采用了Intel的82371芯片,该芯片通过PCI总线与系统北桥相连接,可提供两个IDE接口、两个USB接口并对外提供ISA总线接口。SUPERIO芯片选用了Winbond的W83977,通过ISA总线与南桥连接。系统完整的结构图如图1所示。

从图l中可以看出.龙芯2号与北桥直接用SYSAD64总线连接,并从北桥的SDRAM接口扩展了一个SODIMM槽,可直接使用市场上的笔记本内存条。方便用户进行内存升级和更换,最大可支持到256M。BIOS启动电路从北桥的32位DEVICE口扩展,可支持8位F1lASH或EEPROM为BIOS启动芯片。GT64240支持两个PCI口,在设计中采用了PCI0连接系统南桥芯片。PCI 1连接到PCI Plus插座,用于扩展其他PCl04 Plus模块。南桥和superIO提供了系统的外设接口,并同时将ISA总线扩展到PC104插座。为了提高系统的可靠性,通过北桥的MPP端口(多功能口)扩展了看门狗电路和扬声器电路,可用于系统恢复和报警。

2 关键技术

PC104 Plus系统通常用于对应用空间有较高要求的环境或工业、野外等恶劣环境中,因此要求模块体积小并且可靠性高。以下对系统设计中的关键技术进行阐述。

2.1 电源方案设计

电源是整个系统的关键,电源的性能在很大程度上将直接影响系统的可靠运行。实践经验表明,在工业控制计算机因外部干扰引起的故障中,80%以上都是因为电源的原因产生的。

在本系统中采用单-5V电源供电,可避免由多电压供电带来的潜在不稳定性,其设计示意图如图2所示。其中,1.8V提供给CPU和北桥所需的core电压。3.3V为VIO电压以及sdram等电路的供电电压。为提高系统的可靠性,接在5V电源上的TVS管可实现电路过压保护,而由二极管组成的电路可提供对3.3V和1.8V电源的掉电保护。

为实现板上DC-DC的转换,可考虑采用LDO线性转换电源或开关电源。LDO成本远低于开关电源,但发热量大,使用时需要较大的散热面积,很难满足PCl04主板的散热和工业工作环境温度的要求。因此本设计采用了TI公司的非隔离集成开关电源产品,该电源能正常工作在-40℃~85℃,占用空间小,可直接焊在PCB上使用。另外,由于为集成的产品,免除了用户的调试,可靠性高,非常适合于嵌入式应用,但成本相对较高。

2.2 复位电路

GT64240北桥芯片缺少对龙芯2号CPU进行复位的功能支持,在配套使用时需设计CPU复位电路。同时由于在系统中采用了不同厂家的芯片,因此确定CPU及各个芯片之间的复位顺序也是一个很关键的问题,复位顺序不正确将导致系统不能正常工作。龙芯2号的复位时序如图3所示。为保证时钟的稳定性,应使V∝(CPU IO电压)稳定在3V以上至少lOOms后,再由复位电路向CPU发出VccOK信号,此后确保冷复位信号(ColdReset*)至少持续64K个系统时钟周期,而软复位信号(Reset*)应在冷复位信号无效后至少64个系统时钟周期后置为无效。这样可确保CPU能进入正常工作状态。

为了保证CPU正常的上电复位时序和各个系统芯片之间的复位顺序,设计了如图4所示的系统复位电路。该系统的核心为-EPLD器件EPM7128。电源监控芯片max708在检测到输入电压V∝稳定时给出200ms左右的V∝OK信号,满足系统时钟稳定所需要的至少lOOms的时间。EPLD片内逻辑电路检测到V∞OK信号后,内部计时电路开始工作,准确地给出CPU和所有系统芯片的复位信号。

该方案对系统所有的复位信号统一管理,能确保所有复位信号的正确顺序。EPLD的可重复编程性可方便后期调试和调整,具有很强的灵活性。片内多余的逻辑可用于系统所需的简单逻辑器件,避免了采用过多的分立逻辑器件,在提高系统可靠性的同时节省了PCB空间。

2.3 时钟电路及信号完整性

龙芯2号和GT64240北桥芯片最高工作外频可达133MHz。为了达到这个要求,纯净、稳定的时钟设计以及对关键的高速信号进行信号完整性分析是保证整个系统可靠工作的前提。

为提高时钟电路的稳定性,通过仿真确定了系统各时钟特性阻抗和端接方式,并通过在布线时控制相关时钟信号严格等长来控制传输延迟。图5所示是采用源端匹配方式、驱动信号为133M Plus信号、板级时钟阻抗为50Ω时.扫描匹配电阻从20D~70Ω、步进为5Ω时的反射仿真波形。从图中可以看出,所有时钟波形信号都满足单调性,但在某些区域有较大的过冲。限定过冲在300mV以内,匹配电阻值应在40Ω-55Ω之间,具体可由实际测试结果决定。仿真工具采用的是Cademe的PCB SI。用该工具同时也可对EMI、串扰进行仿真。

除时钟信号外,对所有信号也进行了分析,确定了sysad总线和sdram总线等信号为系统的关键高速信号。对这些关键信号,由于板级布线密度很大,必须考虑串扰、过冲等可能发生的信号完整性问题。这里采取了先期约束布线机制,针对不同的信号制定了相应的布线规范,包括等长信号组、布线间距、最大最小布线长度等。后期通过提取实际布线的拓扑结构进行仿真,根据仿真结果进行布线调整。后期的调试证明了这种方法的可行性。

由于充分考虑到设计中的各个关键环节,基于龙芯2号处理器的PC104 Plus处理器模块一次性投板并调试成功。经过实际测试,能稳定运行中科院计算所为龙芯2号移植的Linux操作系统和相关的测试程序中,并达到系统设计的各项预期目标.现已成功应用于一航空电子视频记录仪中。经过实际应用表明,该处理器模块运行可靠,可推广应用。